TSMC está cerca de adaptar obleas con diseño apilado 3D, a complejos chips de silicio, como procesadores gráficos, utilizando su nueva tecnología patentada de empaquetado Wafer-on-Wafer (WoW), que se introducirá con sus nodos de 7 nm + y 5 nm.

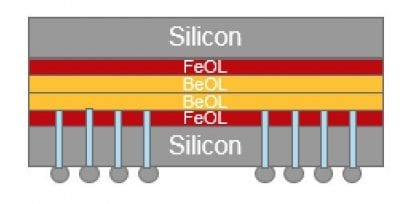

La fabricación de esta arquitectura 3D, se implementa solo en circuitos «menos complejos», como flash NAND, que no corren a temperaturas para nada elevadas, a comparación de complejos sistemas ASIC, como GPU o CPU, los cuales tienen facilidad para sobrecalentar. En su forma actual, TSMC logró apilamientos de 2 capas, en las que ambas capas de silicio son «imágenes espejadas» entre sí (para una alineación perfecta), a través de las cuales pasan los pines de la capa superior.

La vinculación de las dos capas es donde se encuentran la mayor parte de las innovaciones y arquitecturas secretas de TSMC. Para el flash NAND 3D, los chips o pastillas múltiples están cableados a través de sus bordes, no necesitas tantos pines para comunicarte con un circuito NAND, como por ejemplo en un GPU. Para chips complejos, los diseñadores tienen que pasar miles de pines a través de la «capa inferior», el sustrato de conexión y, finalmente, a la «capa superior». Por lo tanto, la capa inferior se desplaza hacia afuera en ambos extremos, un lado se interconecta con el sustrato del paquete para ambos chips, y el lado superior sirve como una especie de sustrato para el silicio superior. Esta innovación es lo que TSMC llama «Vías a través del silicio» (thru-silicon-vias) o TSV.

WoW (oblea en oblea) es diferente de paquete en paquete o PoP (que es la forma en que los SoC y los DRAM se combinan dentro de los teléfonos celulares), en el que dos paquetes completos están cableados concéntricamente en la PCB o con pines en la parte superior Paquete SoC, que interactúa con el paquete DRAM. Un chip WoW se encuentra dentro de un solo paquete y ofrece el doble del área que una pastilla de una sola capa, lo cual seria una ventaja al estar orientado a modelos de alta complejidad, donde se requieren muchos mas pines.

Las capas de unión, no solo ayudan a unir los dos paquetes, sino que también ayudan con la conductividad térmica. Hay una división del trabajo entre los dos chips. La capa inferior debe soportar el cableado de las dos matrices, mientras que la capa superior debe disipar el calor de ambas. En este sentido, la capa superior recibe algo de ayuda del hecho de que tiene áreas en blanco (donde la capa inferior normalmente tendría protuberancias en el sustrato del paquete).